Chapter 8-3. Memory Management III

Paging 기법 (불연속할당)

(OS가 아닌 하드웨어에 의해 수행되는 내용이다.)

물리적인 공간에 올려놓거나 backing store에 올려두거나 할 때 페이지 단위로 시행한다.

프로그램을 구성하는 주소 공간을 같은 크기의 페이지라는 단위로 분할한다.

그리고 Phygical memory를 page와 동일한 크기의 frame으로 나눈다.

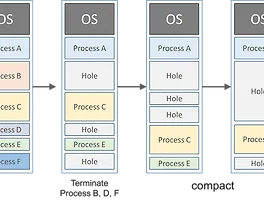

Paging 기법을 사용하면 hole들이 생기지 않는다.

대신에, 불연속으로 할당하게 되면 주소 변환이 복잡해진다.

각각의 페이지들이 물리적인 메모리 중 어느 부분에 올라갔는지 확인해야 하기 때문이다.

그래서 Page 별로 주소 변환을 해줄 방법이 필요해졌고, page table을 생성했다.

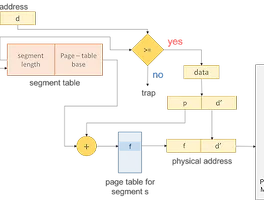

logical address가 table 의 index값을 가리키고,

table index의 value값으로 physical address를 갖는다.

table은 어디에 저장되는가?

프로그램의 주소 공간이 무수히 많은 페이지로 분할되고, 그렇게 되면 table도 무수히 많은 index, value 즉 entry 생성이 필요해진다.

그만큼 용량이 커지기 때문에 레지스터에도, 캐시메모리에도 들어가지 못하는 상황이 된다.

그래서 메모리로 들어가게 된다.

메모리에 접근하기 위해서 우선 페이지 테이블에 접근을 하고 다시 물리적인 메모리로 접근하는 방식이 되었다.

메모리에 두 번 접근해야 하는 것이다.

오히려 더 느려지는 상황이 발생했다.

이를 해결하기 위해서 레지스터를 사용한다.

Page-table base registser가 메모리 상의 page table의 주소 값을 갖고 있고,

Page-table length register가 테이블의 크기를 보관한다.

그리고 Associative register와 TLB(Translation Look-aside Buffer)를 사용한다.

일종의 캐시 메모리로, 주소변환을 위한 캐시메모리이다.

TLB에는 빈번하게 참조되는 page table의 일부를 저장해둔다.

CPU로부터 논리적인 주소를 통해 요청이 들어오면 일단 TLB를 점검한다.

요청한 주소에 해당하는 내용이 존재한다면(TLB hit), 바로 TLB를 통해 주소 변환이 이루어진다.

존재하지 않는다면(TLB miss), page table로 접근하여 주소 변환이 이루어진다.

TLB를 사용하는데에도 문제점이 존재한다.

TLB는 논리적인 페이지 번호와 물리적인 페이지 번호 두 가지의 값을 저장하고 있어야 한다.

그리고 바로 논리적인 주소로 Offset 접근을 할 수 있는 것이 아니라,

TLB전체를 모두 검색해봐야 하는 것이다.

(이는 Order of n 의 time complexity를 발생시킨다.)

그래서!

위에서 언급한 Associative register를 이용한다.

이 레지스터는 Parallel search를 통해서 전체를 한 번에 검색해 time complexity를 O(1)로 낮춘다.

Chapter 8-3. 끝

이 포스팅은 이화여대 반효경 교수님 강의를 듣고 요약한 내용을 담고 있습니다.

'Dev.Basic > 운영체제' 카테고리의 다른 글

| [OS] 8-5. Memory Management V (0) | 2016.06.06 |

|---|---|

| [OS] 8-4. Memory Management IV (1) | 2016.06.05 |

| [OS] 8-2. Memory Management II (0) | 2016.06.05 |

| [OS] 8-1. Memory Management I (0) | 2016.06.05 |

| [OS] 7. Deadlock (0) | 2016.06.04 |